【導(dǎo)讀】在摩爾定律的推動(dòng)下,集成電路工藝取得了高速發(fā)展,單位面積上的晶體管數(shù)量不斷增加。片上系統(tǒng)(System-on-Chip,SoC)具有集成度高、功耗低、成本低等優(yōu)勢,已經(jīng)成為大規(guī)模集成電路系統(tǒng)設(shè)計(jì)的主流方向,解決了通信、圖像、計(jì)算、消費(fèi)電子等領(lǐng)域的眾多挑戰(zhàn)性的難題。

1. 概述

在摩爾定律的推動(dòng)下,集成電路工藝取得了高速發(fā)展,單位面積上的晶體管數(shù)量不斷增加。片上系統(tǒng)(System-on-Chip,SoC)具有集成度高、功耗低、成本低等優(yōu)勢,已經(jīng)成為大規(guī)模集成電路系統(tǒng)設(shè)計(jì)的主流方向,解決了通信、圖像、計(jì)算、消費(fèi)電子等領(lǐng)域的眾多挑戰(zhàn)性的難題。 隨著片上系統(tǒng)SoC的應(yīng)用需求越來越豐富,SoC需要集成越來越多的不同應(yīng)用的IP(Intellectual Property)。另外,片上多核系統(tǒng)MPSoC(MultiProcessor-System-on-Chip)也已經(jīng)成為必然的發(fā)展趨勢。

隨著SoC的高度集成以及MPSoC的高速發(fā)展,對(duì)片上通信提出了更高的要求。片上網(wǎng)絡(luò)技術(shù)(Network-on-Chip,NoC)在這個(gè)時(shí)候也得到了極大的應(yīng)用,它本質(zhì)上就是提供一種解決芯片內(nèi)不同IP或者不同核心之間數(shù)據(jù)傳輸?shù)钠贤ㄐ欧桨浮?/div>

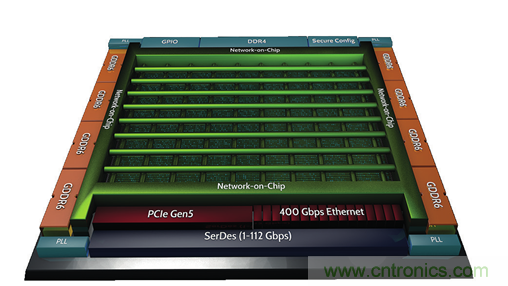

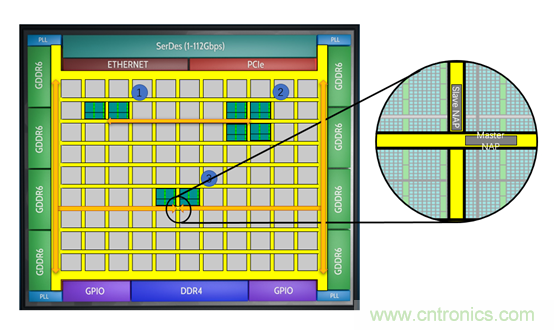

片上網(wǎng)絡(luò)技術(shù)從發(fā)明至今已有20多年的歷史,在SoC中已經(jīng)有了廣泛的應(yīng)用。針對(duì)片上網(wǎng)絡(luò)高帶寬、低延遲的特性,主流FPGA公司也開始考慮將NoC用于高端FPGA中來解決數(shù)據(jù)傳輸?shù)母邘捫枨蟆chronix的新一代7nm工藝的Speedster 7t便是最早集成了NoC的高端FPGA之一。如圖1所示。

圖1 Speedster 7t FPGA結(jié)構(gòu)圖

2. 片上互連架構(gòu)的發(fā)展

片上互聯(lián)架構(gòu)的發(fā)展主要經(jīng)歷了三個(gè)階段:共享總線(Bus)、Crossbar以及片上網(wǎng)絡(luò)(NoC)[1]。

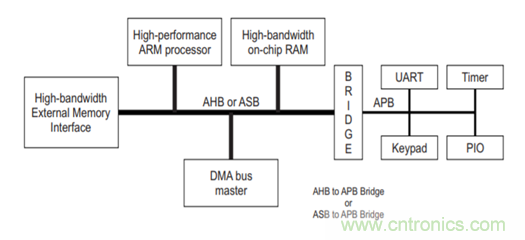

(1) 傳統(tǒng)的SoC片上通信結(jié)構(gòu)一般采用共享總線的方式。在共享總線結(jié)構(gòu)中,所有的處理器和IP模塊共享一條或多條總線。當(dāng)有多個(gè)處理器同時(shí)訪問一條總線時(shí)候需要有仲裁機(jī)制來決定總線的所有權(quán)。共享總線片上通信系統(tǒng)結(jié)構(gòu)一般比較簡單,且硬件代價(jià)也小。但是帶寬有限,而且?guī)捯矝]法隨著IP的增多而進(jìn)行擴(kuò)展。1996年,ARM公司提出的AMBA總線廣泛應(yīng)用于嵌入式微處理器的片上總線,現(xiàn)在已經(jīng)成為事實(shí)上的工業(yè)標(biāo)準(zhǔn)。

圖2 典型的AMBA總線系統(tǒng)[2]

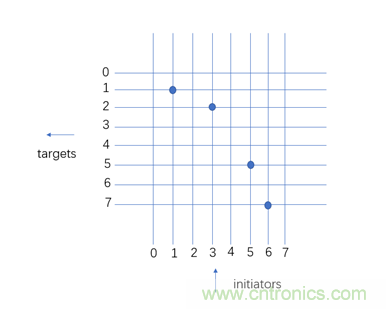

(2) 對(duì)于傳統(tǒng)的共享總線,當(dāng)多個(gè)處理器同時(shí)去訪問不同的IP的時(shí)候,因?yàn)樾枰俨脵C(jī)制去決定總線的所有權(quán),所以傳統(tǒng)的總線方式在這種情況下就會(huì)造成一定的瓶頸,最大的問題就是訪問的延時(shí)。在這種情況下,為了滿足多處理同時(shí)訪問的需求同時(shí)提高整個(gè)系統(tǒng)的帶寬,一種新的解決方案Crossbar孕育而生,如圖3所示一個(gè)典型的Crossbar結(jié)構(gòu)。

Crossbar保證了多路通信同時(shí)進(jìn)行的實(shí)時(shí)性,只要不是訪問同一個(gè)目標(biāo)設(shè)備,就不需要用到仲裁,大大減少了因?yàn)橹俨脦淼钠款i問題。但是隨著設(shè)備數(shù)的增加,Crossbar的規(guī)模會(huì)以幾何級(jí)數(shù)增長。所以通常我們通過橋接設(shè)備去級(jí)聯(lián)多個(gè)Crossbar來支持設(shè)備的擴(kuò)展。但是橋接設(shè)備可能會(huì)成為系統(tǒng)的瓶頸,增加傳輸?shù)难舆t。

圖3 典型的單向8x8 Crossbar

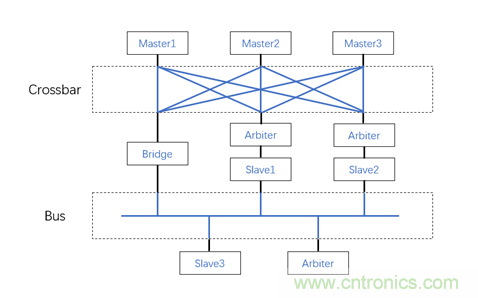

實(shí)際應(yīng)用中,我們通常也會(huì)采用Crossbar和共享總線相結(jié)合的方式,用橋接器將Crossbar網(wǎng)絡(luò)和共享總線網(wǎng)絡(luò)連接起來,如圖4所示一個(gè)典型的混合型拓?fù)浣Y(jié)構(gòu)。

圖4 典型的混合拓?fù)渚W(wǎng)絡(luò)

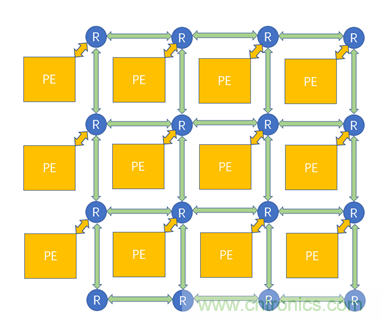

(3) 片上網(wǎng)絡(luò)NoC帶來了一種全新的片上通信方法,顯著優(yōu)于傳統(tǒng)的總線式和Crossbar的性能。NoC是一種可擴(kuò)展性更好的設(shè)計(jì)。在NoC架構(gòu)中,每一個(gè)模塊都連接到片上路由器,模塊傳輸?shù)臄?shù)據(jù)則是形成了一個(gè)個(gè)數(shù)據(jù)包,通過路由器去送達(dá)數(shù)據(jù)包的目標(biāo)模塊。如圖5所示是一個(gè)典型的NoC結(jié)構(gòu),圖中的R表示Router, 所有的Router可以是同步,但每個(gè)Router所連接的PE(Processing Element)與Router異步,自成一個(gè)時(shí)鐘域(Clock Domain)。所以基于NoC的系統(tǒng)能更好地適應(yīng)在復(fù)雜多核SoC設(shè)計(jì)中使用的全局異步局部同步時(shí)鐘機(jī)制。另外,NoC可以支持各種擴(kuò)展功能,比如流量控制(flow control)、服務(wù)質(zhì)量(QoS)等等。 因此,NoC是多核系統(tǒng)的最佳互聯(lián)機(jī)制。

圖5 典型的片上網(wǎng)絡(luò)NoC結(jié)構(gòu)

3. NoC在高端FPGA的應(yīng)用

FPGA在日益增長的數(shù)據(jù)加速需求上正在發(fā)揮越來越重要的作用。為了滿足云計(jì)算和邊緣計(jì)算中各種高性能應(yīng)用的需求,F(xiàn)PGA作為一種可編程可定制化的高性能的器件逐步成為一條部署高吞吐量數(shù)據(jù)加速的快捷途徑。但同時(shí)這些高性能的加速應(yīng)用也對(duì)高端FPGA提出了更高的要求,高算力、高帶寬的數(shù)據(jù)傳輸以及高帶寬的存儲(chǔ)器。

片上網(wǎng)絡(luò)技術(shù)已經(jīng)比較廣泛的用于SoC中,并取得了比較好的效果。近年來才慢慢用于FPGA中,Achronix創(chuàng)建了一種可最大限度地提高系統(tǒng)吞吐量的Speedster 7t FPGA芯片,創(chuàng)新地將二維片上網(wǎng)絡(luò)(2D NoC)運(yùn)用到了FPGA中,可以在邏輯陣列內(nèi)的處理單元與各種片上高速接口和存儲(chǔ)器接口之間高速地傳輸數(shù)據(jù),真正實(shí)現(xiàn)了數(shù)據(jù)密集型應(yīng)用吞吐量的最大化。有了片上網(wǎng)絡(luò)的FPGA如虎添翼,帶來了傳統(tǒng)FPGA所不及的很多優(yōu)勢,勢必在各種數(shù)據(jù)加速應(yīng)用中發(fā)揮巨大的作用。

4. NoC給Speedster 7t FPGA帶來的優(yōu)勢

Achronix Speedster 7t FPGA擁有支持單通道速率112Gbps的SerDes、400G以太網(wǎng)MAC、PCIe GEN5控制器以及帶寬高達(dá)4Tbps帶寬的GDDR6控制器,為各種數(shù)據(jù)加速應(yīng)用提供了高帶寬的I/O接口和高帶寬的存儲(chǔ)器。在這類應(yīng)用中,會(huì)有大量的數(shù)據(jù)進(jìn)入FPGA進(jìn)行處理,處理后的數(shù)據(jù)會(huì)通過FPGA輸出,所以除了FPGA算力以外,數(shù)據(jù)移動(dòng)速度直接決定了器件的性能以及用戶的體驗(yàn)。為了提高數(shù)據(jù)傳輸速率,Achronix在Speedster 7t FPGA中專門設(shè)計(jì)了不同于傳統(tǒng)FPGA數(shù)據(jù)移動(dòng)通道的片上網(wǎng)絡(luò)。如圖6所示。這是一個(gè)可橫跨和垂直跨越FPGA邏輯陣列的創(chuàng)新性的、高帶寬的二維片上網(wǎng)絡(luò)(2D NoC),它不僅可以連接到所有FPGA高速接口、高帶寬存儲(chǔ)器接口,還可以作為內(nèi)部邏輯之間的互連。

圖6 Speedster 7t片上網(wǎng)絡(luò)(NoC)結(jié)構(gòu)

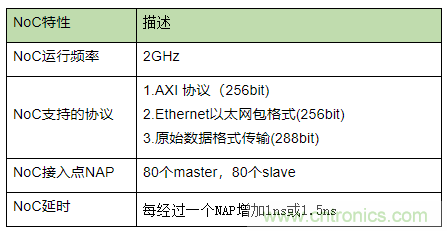

Speedster 7t FPGA上的二維片上網(wǎng)絡(luò)(2D NoC)不是由可編程邏輯搭建,而是固化的ASIC邏輯實(shí)現(xiàn),固定運(yùn)行頻率為2GHz,每一行或者每一列的NoC都可以作為兩個(gè)單向256位實(shí)現(xiàn)雙向的通路,所以每個(gè)方向可提供512Gbps的帶寬,整個(gè)網(wǎng)絡(luò)總帶寬則能達(dá)到27Tbps。

下面的表格列出了Speedster 7t FPGA中NoC的特性。

表1 Speedster 7t FPGA中NoC特性

NoC為FPGA提供了以下幾項(xiàng)重要優(yōu)勢:

(1) 大幅提高設(shè)計(jì)性能,解決一些高性能應(yīng)用如400G以太網(wǎng)的性能瓶頸:通常在數(shù)據(jù)流經(jīng)過400G以太網(wǎng)MAC解包以后會(huì)是一個(gè)超高位寬且需要運(yùn)行在很高頻率的處理,這在傳統(tǒng)FPGA邏輯單元里面是無法實(shí)現(xiàn)的,而NoC就能解決性能瓶頸。我們會(huì)在后續(xù)文章具體說明。

(2) NoC是在傳統(tǒng)可編程邏輯之外額外增加的走線資源,所以在高資源占用設(shè)計(jì)中可以降低布局布線擁塞的風(fēng)險(xiǎn)。

(3) NoC包含了異步時(shí)鐘轉(zhuǎn)換,仲裁控制等邏輯,可以去替代傳統(tǒng)的邏輯去做高速接口和總線管理等,所以利用NoC可以簡化用戶設(shè)計(jì)節(jié)省一部分傳統(tǒng)資源(LE、FIFO和布線等)的使用。

(4) NoC部分是ASIC固化邏輯,功耗比傳統(tǒng)的FPGA可編程邏輯實(shí)現(xiàn)要低很多。

(5) 利用NoC可以實(shí)現(xiàn)真正的模塊化設(shè)計(jì)。傳統(tǒng)高端FPGA設(shè)計(jì)通常是需要一個(gè)FPGA工程師團(tuán)隊(duì)來完成,每個(gè)工程師設(shè)計(jì)自己模塊,在FPGA整個(gè)芯片里調(diào)試驗(yàn)證自己模塊,然后再把各個(gè)模塊連接成更大的完整設(shè)計(jì),這時(shí)候會(huì)由于資源占用上升,通常需要花很多時(shí)間去優(yōu)化布局甚至去修改設(shè)計(jì)以達(dá)到目標(biāo)性能。而在Achronix Speedster7t 中可以讓模塊之間通過NOC互聯(lián),再借助對(duì)于單個(gè)模塊功能性能調(diào)試完成后固定布局技術(shù),甚至可以達(dá)到NoC互聯(lián)后整體設(shè)計(jì)不需要額外聯(lián)調(diào)的可能。這樣可以大幅減少研發(fā)工作量和時(shí)間。

后面我們會(huì)繼續(xù)深入了解Speedster 7t FPGA上的二維片上網(wǎng)絡(luò)(2D NoC),并且會(huì)用一些具體的設(shè)計(jì)來講解如何在Speedster 7t FPGA上使用NoC以及NoC給FPGA設(shè)計(jì)帶來的好處,敬請(qǐng)期待。 如需更多信息或者有任何疑問您可以通過Achronix公眾號(hào)里聯(lián)系方式聯(lián)系我們,也可訪問Achronix公司官方網(wǎng)站 http://www.achronix.com

參考文獻(xiàn):

1.The SoC Interconnect Fabric: A Brief History by Kurt Shuler 2013

2.AMBA specification 2.0

3.A comparison of Network-on-Chip and Busses by Arteris

4.片上通信結(jié)構(gòu)-共享總線和NoC的分析與比較 周文彪,張巖,毛志剛 2007

5.Achronix website www.achronix.com

(來源:Achronix,作者:Achronix資深現(xiàn)場應(yīng)用工程師——黃侖)

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請(qǐng)聯(lián)系小編進(jìn)行處理。