【導讀】近來,業(yè)界對于隔離式 DC-DC 穩(wěn)壓器中高頻變壓器的性能要求愈發(fā)嚴苛,尤其是在抗電磁干擾 (EMI) 方面。在本系列文章的第 7 部分[1-7] 中,我們詳細探討了隔離式反激穩(wěn)壓器中共模 (CM) 噪聲的主要來源和傳播路徑。

高瞬態(tài)電壓 (dv/dt) 開關節(jié)點是共模噪聲的主要來源,而變壓器的繞組間分布電容則是共模噪聲的主要耦合路徑。在第 7 部分中,我們在簡單方便的雙電容變壓器模型基礎上,采用共模噪聲等效電路來模擬流經(jīng)變壓器電容的位移電流。在此期間,僅需使用一個信號發(fā)生器和一個示波器即可提取寄生電容并確定變壓器共模噪聲性能的特征,而無需進行在線測試。

在第 8 部分,我們將探討隔離式 DC/DC 電路的共模噪聲抑制方法。工作在高輸入電壓下的轉(zhuǎn)換器(例如,電動汽車車載充電系統(tǒng)、數(shù)據(jù)中心電源系統(tǒng)和射頻功放電源中的相移式全橋轉(zhuǎn)換器[8] 和 LLC 串聯(lián)諧振轉(zhuǎn)換器[9])會產(chǎn)生較大的共模電流。在采用氮化鎵開關器件時,這種情況更為明顯,因為此類器件的開關速度 dv/dt 高于硅材質(zhì)的同類器件。

對于隔離式設計,有多種抑制共模噪聲的方法,包括采用對稱的電路布局、在初級側(cè)接地端與次級側(cè)接地端之間連接一個電容、加入屏蔽層、增加平衡電容、優(yōu)化變壓器繞組設計以及使用可調(diào)節(jié)共模噪聲消除輔助繞組。本文將以反激電路為重點,逐一解讀這些方法。

對稱式電路設計

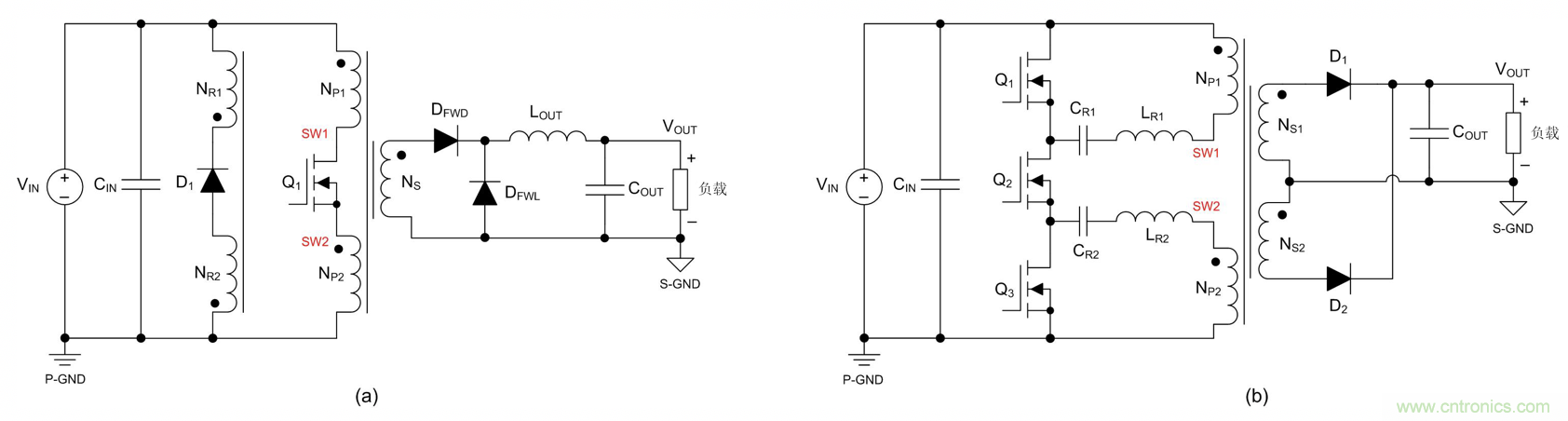

在對稱式拓撲結構中,與地之間形成互補電勢的開關節(jié)點成對出現(xiàn)。如果關聯(lián)寄生電容相同,則產(chǎn)生的共模位移電流基本可以相互抵消。圖 1a 為雙開關正激轉(zhuǎn)換器(例如德州儀器 (TI) 的 LM5015)的原理圖[10,11]。圖 1b 為采用分立式初級側(cè)和次級側(cè)繞組的反激轉(zhuǎn)換器。這兩種轉(zhuǎn)換器的初級側(cè)電路均采用對稱式設計,具有異相電壓開關波形(SW1 和 SW2),可產(chǎn)生相反極性的共模電流,從而降低總共模噪聲。

圖 1:平衡繞組拓撲結構,采用對稱式初級側(cè)電路和等幅異相 dv/dt 開關波形,具有更低共模噪聲:(a) 雙開關正激轉(zhuǎn)換器;(b) 采用分立式初級和次級繞組的反激轉(zhuǎn)換器

圖 1a 為雙開關正激轉(zhuǎn)換器的拓撲結構,盡管這種結構早已為人所熟知,但其在共模噪聲抑制方面的優(yōu)勢卻并未得到充分重視。圖 1b 為平衡繞組反激轉(zhuǎn)換器,其次級繞組同樣采用對稱式設計。分立式繞組通??梢越诲e纏繞,以降低漏電感。這種電路的主要缺點是需要一個以 SW2 為基準點的浮動柵極驅(qū)動器。

對于單開關正激轉(zhuǎn)換器和 LLC 諧振轉(zhuǎn)換器拓撲,也可以采用類似的對稱式平衡繞組設計,如圖 2 所示。改進后的對稱電路需要額外增加一些元件,例如正激轉(zhuǎn)換器中的浮動柵極驅(qū)動器和 LLC 諧振電路中的附加開關,并且只有在變壓器的物理繞組結構產(chǎn)生對稱的寄生電容時才會產(chǎn)生共模衰減的效果。因此通常情況下,需要采用其他方法來抑制共模噪聲,并使用傳統(tǒng)的隔離式拓撲電路。

圖 2:對單開關正激轉(zhuǎn)換器 (a) 和 LLC 諧振轉(zhuǎn)換器 (b) 采用對稱式初級側(cè)繞組設計

在初級地與次級地之間連接一個電容

在三線 AC-DC 應用中,通常會在 EMI 輸入濾波器中通過一個 Y 電容將火線和零線連接到機箱地,用以衰減共模噪聲。但在雙線 DC-DC 系統(tǒng)中,由于沒有機箱地連接點,因此無法連接 Y 電容。在這類系統(tǒng)中,可以在初級側(cè)接地端 (P-GND) 與次級側(cè)接地端 (S-GND) 之間連接一個替代電容,將傳播到次級側(cè)的共模電流分流回初級側(cè)。

請參見第 7 部分圖 1 中的 CZ 電容。該元件是一種安全級電容,額定電壓為 1 kV 或更高,遠高于所需的隔離電壓規(guī)格。然而這種電容一旦在故障狀況下出現(xiàn)短路,就會大大影響電流隔離效果。此外,如果 S-GND 連接的共模電壓擺幅相對于初級側(cè)過大(例如在高側(cè)柵極驅(qū)動器偏置電源應用中),電容傳導的電流就會過大。同時,如果 DC-DC 級的前端是一個 AC-DC 前端整流器,則該電容可能會傳導工頻泄漏電流,這在實際應用中可能是不允許的,也是受到監(jiān)管要求限制的[12-15]。

共模噪聲的平衡與消除方法

平衡方法分為變壓器內(nèi)部平衡和外部平衡,可以降低與變壓器繞組電容相關的共模噪聲。內(nèi)部平衡方法包括應用屏蔽層[16-18]、優(yōu)化繞組設計以及使用噪聲消除繞組。而外部平衡方法最常見的是在所選初級和次級繞組端子之間加入一個平衡電容[12]。

屏蔽

屏蔽方法通過插入導線或金屬箔屏蔽層來降低流經(jīng)繞組間電容的位移電流,從而阻止變壓器初級側(cè)繞組與次級側(cè)繞組之間的近場耦合。

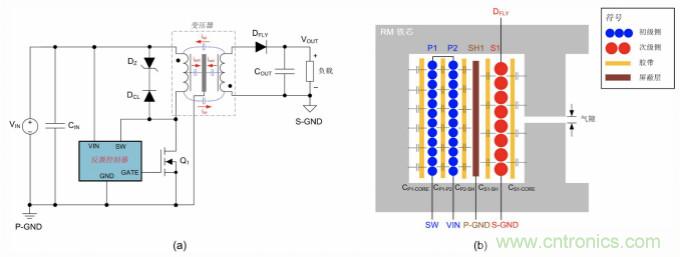

例如,圖 3a 是一個反激轉(zhuǎn)換器,其初級側(cè)與次級側(cè)之間加入了一個傳統(tǒng)的單匝金屬箔屏蔽繞組。圖 3b 是 RM 型磁芯的示意圖,磁芯配有帶氣隙的中柱和垂直放置的繞組。在這半個繞組窗口中,共有兩個串聯(lián)的初級層 (2 x 12T)、一個次級層 (1 x 8T) 和一個屏蔽層。繞組采用非交錯式分層布局,分為 P1、P2、SH1 和 S1 四層。圖中還顯示了繞組層間寄生電容。

圖 3:(a) 反激轉(zhuǎn)換器,其初級層與次級層之間帶有傳統(tǒng)的金屬箔靜電屏蔽繞組,該屏蔽層連接到 P-GND;(b) 變壓器繞組窗口內(nèi)的繞組層結構

在初級層 P2 與次級層 S1 之間,加入了一個單屏蔽層 SH1。該屏蔽層通常連接回初級側(cè)電路中的靜態(tài)電位點,例如圖 3 所示的本地 P-GND 或輸入電容的正極端子,即靜態(tài)交流節(jié)點。這樣可以阻止 P2 和 S1 之間的電耦合,并消除 P2 與 S1 之間的位移電流。

加入屏蔽層后,ipsh 將經(jīng)由屏蔽層返回 P-GND,而不是流經(jīng)輸出端而返回機箱地。但是,屏蔽層與相鄰次級繞組之間的電容依然存在。由于單匝屏蔽繞組與次級繞組的感應電壓存在差異(單匝次級繞組除外),因此在屏蔽層與次級繞組之間必然存在共模電流??筛挠幂o助繞組的抽頭來驅(qū)動屏蔽繞組,使屏蔽繞組的平均電壓與次級繞組的平均電壓相符,以實現(xiàn)共模平衡[18]。

注意,由于磁芯采用高介電常數(shù)材料,圖 3 中 P1 層和 S1 層之間會存在耦合。所以,盡管單屏蔽層有助于減弱共模噪聲,但并不能徹底消除。此外,還有一個缺點是,隨著初級側(cè)與次級側(cè)間邊界數(shù)量的增加,需要的屏蔽層也越來越多。重要的是,屏蔽層會增大繞組之間的空間,從而導致漏電感增加。通常而言,應盡可能減小銅箔屏蔽層的厚度,以減少因鄰近效應引起的渦流損耗。在高開關頻率下,屏蔽層中的損耗會變得過大,而且屏蔽層也會使反射到開關節(jié)點的總寄生電容增大。

平衡電容的值與位置

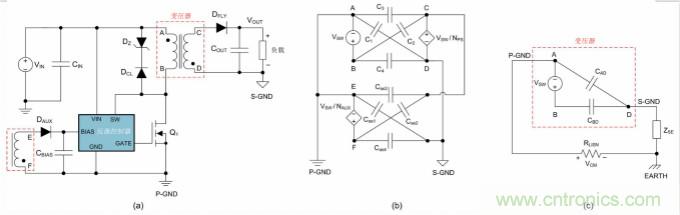

圖 4a 為帶初級側(cè)、次級側(cè)和輔助變壓器繞組的反激轉(zhuǎn)換器的原理圖。NPS 和 NAUX 分別代表初級側(cè)與次級側(cè)繞組匝數(shù)比以及初級側(cè)與輔助繞組匝數(shù)比。對于初級側(cè)繞組與輔助繞組而言,由于電流僅在初級側(cè)流動,對共模噪聲不產(chǎn)生影響,因此不考慮這兩者之間的耦合。在第 7 部分中我們曾討論過,通過兩個 4 電容電路即可對初級側(cè)繞組與次級側(cè)繞組之間以及輔助繞組與次級側(cè)繞組之間的耦合進行建模(如圖 4b 所示)。

圖 4: (a) 帶輔助繞組的反激轉(zhuǎn)換器;(b) 三繞組反激變壓器的集總共模寄生電容模型;(c) 使用雙電容變壓器模型的共模噪聲等效電路

如果輸入電容對共模噪聲呈現(xiàn)低阻抗特性,則初級側(cè)繞組的端子 A 與 P-GND 之間短路??梢允褂煤喕碾p電容變壓器模型,再以 ZSE 模擬 S-GND 與大地之間的電容耦合,最終的共模噪聲等效電路模型見圖 4c(有關更多相關信息和描述,請參見第 7 部分)。

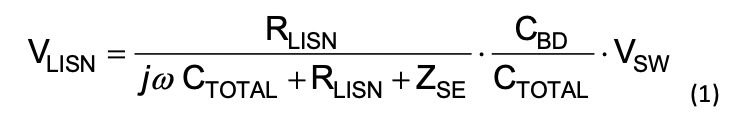

公式 1 用于計算線路阻抗穩(wěn)定網(wǎng)絡 (LISN) 中的共模噪聲電壓。從中可以看出,降低電容 CBD 可以使噪聲電壓降低。

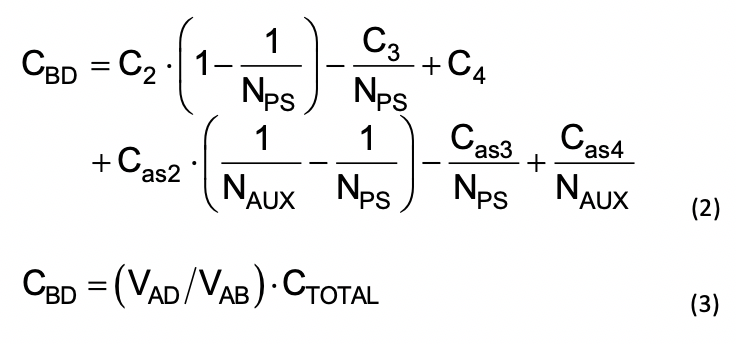

公式 2 是 CBD 的理論表達式,該值可使用第 7 部分介紹的方法基于公式 3 進行計算:

可以通過增大公式 2 中各負項的值,將 CBD 平衡為零[13]。最簡單的方法是在初級側(cè)和次級側(cè)間變壓器端子 A 和 C 之間的 C3 上并聯(lián)一個電容。這一外部平衡電容的值為 CEXT = NPSCBD。

同樣,如果 CBD 為負值(VAD 和 VAB 電壓異相),則在端子 B 與 D 之間的 C4 上并聯(lián)一個等于 |CBD| 的平衡電容,可實現(xiàn)平衡。注意,根據(jù)公式 3,如果測得的 VAD 為零,則 CBD 也相當于零,基本消除了通過變壓器的共模噪聲。這是非常方便的測試變壓器是否平衡的手段。

繞組設計

除了使用平衡電容外,還可以通過調(diào)整變壓器繞組層的位置,來優(yōu)化共模平衡。根據(jù)成對繞組層的設計理念[12-15],變壓器初級側(cè)和次級側(cè)的層具有相似的 dv/dt,因此,這些層的交錯重疊不會產(chǎn)生共模噪聲。繞組間電容兩端的平均電壓具有相似的幅值和極性,也可以最大程度減小甚至消除流經(jīng)電容的共模電流。

一個最基本的原則就是,確保相鄰的初級側(cè)繞組層與次級側(cè)繞組層具有相似的電壓分布。如果繞組間寄生電容均勻分布于兩個成對繞組層之間,可以使電容的 dv/dt 保持為零,這樣便不會產(chǎn)生共模電流。

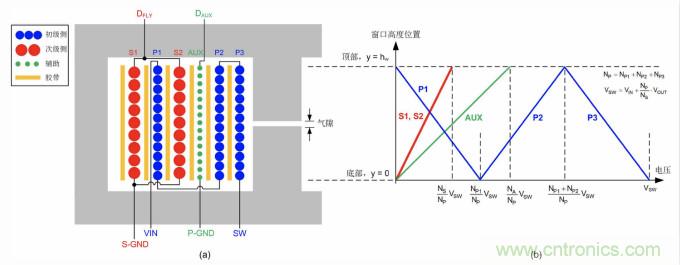

以圖 4a 的反激轉(zhuǎn)換器為例,其變壓器為交錯式三繞組(初級側(cè)、次級側(cè)、輔助)變壓器。盡管交錯式設計會增大繞組間電容,但出于降低漏電感和鄰近效應損耗的考慮,必須采用這種設計。圖 5a 是反激變壓器的半個繞組窗口,該變壓器包含三個串聯(lián)初級層 (3 x 12T)、兩個并聯(lián)次級層 (2 x 9T) 和一個輔助/偏置繞組層 (1 x 15T)。

圖 5: (a) 采用夾層繞組層結構的反激變壓器;(b) 繞組窗口內(nèi)各繞組層的電壓分布

圖 5b 為在電壓沿繞組線性分布情況下的繞組電壓分布圖。為最大程度降低共模噪聲,應使初級側(cè)繞組層與次級側(cè)繞組層之間相鄰繞組層的平均電壓差達到最低。因此如圖 5a 所示,將交錯繞組層的排列順序設計為 S1-P1-S2-AUX-P2-P3。

采用如圖 5a 所示的端子連接時,P1 與 S1 或 S2 之間的平均電壓差最低。如圖 5a 所示,P1 始于 VIN(靜態(tài)節(jié)點),與兩個并聯(lián)次級層 S1 和 S2 相鄰。與之類似,AUX 繞組與 S2 層相鄰,因為 AUX 與 S2 之間的電壓差小于 S2 與 P2 或 P3 之間的電壓差。由于 AUX 與 P2 繞組均位于初級側(cè),因此兩者之間的電壓差不會產(chǎn)生共模噪聲。兩者之間的位移電流同樣在轉(zhuǎn)換器初級側(cè)流動,不會被 LISN 視為 EMI。相反,如果采用 P1-S1-P2-S2-AUX-P3 這種完全交錯的繞組結構,由于 S1 與 P2 以及 P2 與 S2 這兩對繞組層之間的平均電壓差增大,共模噪聲將明顯增強。

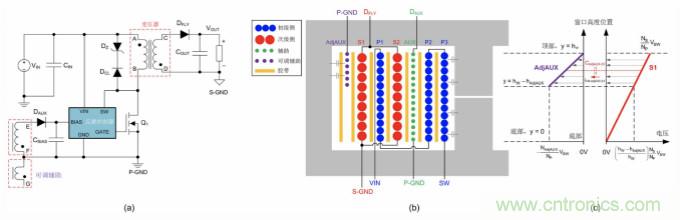

可調(diào)節(jié)噪聲消除輔助繞組

圖 6 中的 AdjAUX 是一個可調(diào)節(jié)噪聲消除輔助繞組層,纏繞在次級層 S1 的外側(cè),用以平衡繞組層內(nèi)未完全消除的共模噪聲[13,14]。AdjAUX 的一個端子連接到 P-GND,另一個端子處于懸浮狀態(tài)。

圖 6: (a) 在外層增加可調(diào)節(jié)輔助繞組用以消除共模噪聲的原理圖;(b)繞組排列情況;(c) 電壓和電流分布

由于 AdjAUX 與 S1 之間的電壓差為負值,因此位移共模電流從 S1 流向 AdjAUX 繞組,再流回初級側(cè)。由于 P1 與 S1、P1 與 S2 以及 AUX 與 S2 層之間的電壓差為正值(本例中 P1 和 AUX 的匝數(shù)多于 S1 和 S2 的匝數(shù)),因此這樣有助于消除從 P1 流向 S1 和 S2 以及從 AUX 流向 S2 的位移共模電流。如圖 6b 所示,AdjAUX 繞組位于變壓器繞組的外層,因此可以方便地通過調(diào)整匝數(shù)來有效消除噪聲。

如圖 6c 所示,當 AdjAUX 繞組始于繞組窗口的頂部時,AdjAUX 與 S1 層之間的電壓差最大,需要較少匝數(shù)來達到消除噪聲的效果,而如果 AdjAUX 繞組位于窗口底部,則需要的匝數(shù)就會更多。

由于 AdjAUX 繞組不靠近氣隙,會產(chǎn)生零磁場,因而沒有渦流功率損耗。這樣,變壓器交流繞組損耗低于采用傳統(tǒng)屏蔽層時的損耗。同時,由于繞組層之間沒有屏蔽層,繞組間的互耦增高,使得漏電感降低[18]。最后,可以結合第 7 部分介紹的變壓器平衡檢測技術,來方便地設計 AdjAUX 繞組層,無需任何在線測試。

總結

共模噪聲是高頻隔離式 DC/DC 轉(zhuǎn)換器設計中需要重點關注的問題。為了提高功率密度,設計師們往往會考慮增大開關頻率。而隨著開關頻率的增大,初級側(cè)開關節(jié)點的高 dv/dt 以及通過變壓器繞組間電容的相關共模干擾已經(jīng)給系統(tǒng)帶來不利影響。要降低共模噪聲,可以采用對稱式拓撲設計、加入屏蔽層以及平衡電容等方法。在進行繞組設計時,也可以通過正確布置變壓器層以及在繞組層端子與電路節(jié)點間選擇最優(yōu)的連接,來達到降噪的目的。此外,在變壓器外側(cè)纏繞輔助的噪聲消除繞組也可以平衡共模噪聲。對于某些拓撲結構,可以單獨這些方法,而為了滿足規(guī)范要求并解決復雜的共模噪聲問題,也可以發(fā)揮這些方法的組合優(yōu)勢,以達到提高降噪效果的目的。

免責聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯(lián)系小編進行處理。

推薦閱讀: